SLVS-EC Receiver IP

SLVS-EC Receiver IP

SLVS-ECとは

SLVS-EC(Scalable Low Voltage Signaling with Embedded Clock)はソニーのCMOS イメージセンサに実装される高速・高性能シリアルインターフェースです。従来のLVDSとは異なり、データにクロックを埋め込まれているため、シリアルバス間のスキューを意識せずに基板設計を行うことが可能です。

「より速く、よりローパワーで、より簡単に」を実現する新しいインターフェース。それが SLVS-EC です。

SLVS-EC Receiver IP 概要

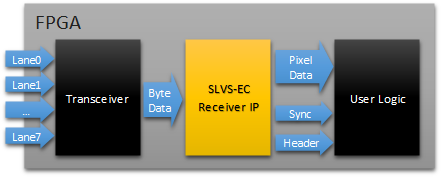

シーアイエスでは FPGA の高速トランシーバを経由して受信したバイトデータからピクセルデータを抽出することに特化し、リソースの使用量がより少ない IP を開発致しました。FPGA の内部クロックやデータバス構成はアプリケーションによって様々ですが、本 IP とお客様のロジックを組み合わせるなら、トータルのリソース使用量を最適化することが可能です。また新たにペイロードのエラー検出やエラー訂正(オプション)にも対応しております。

製品の仕様

スペック表

| SLVS-EC Version | 2.0 準拠 |

|---|---|

| Lane | 1,2,4,6,8 |

| Raw Format | 8,10,12,14,16 |

| Line Length | 4~∞(default 65532) |

| CRC | 対応 |

| ECC | 対応(オプション) |

| Baud Rate | Grade1~3 |

| Multi Stream | 非対応 |

| Output Signals | ピクセルデータ、同期信号、ヘッダ情報等 |

リソース使用量

CISのSLVS-EC Receiver IPの特徴の1つはリソース使用量が少ないことです。本IPではリソース使用量に影響するSLVS-ECのレーン数をダイナミックに変更できますが、使用する最大レーン数を制限するか、固定レーン構成にすることにより、更にリソースを削減できます。以下は各構成のリソース使用量(Artix7、Vivado2022.1)です。他のデバイス、ツールを使用した場合のリソース使用量についてはお問い合わせください。

可変レーン(括弧内はECC対応)

| Resource | Max.2Lane | Max.4Lane | Max.8Lane |

| LUT | 1116(2681) | 1761(3829) | 4165(6927) |

|---|---|---|---|

| FF | 904(2351) | 1253(3081) | 1965(4523) |

| BRAM | 0(2.5) | 0(2.5) | 0(3.5) |

固定レーン(括弧内はECC対応)

| Resource | 1Lane | 2Lane | 4Lane | 6lane | 8lane |

| LUT | 887(2181) | 971(2430) | 1323(3400) | 2723(5576) | 2290(5412) |

|---|---|---|---|---|---|

| FF | 807(2250) | 863(2308) | 1155(2985) | 1777(4329) | 1816(4369) |

| BRAM | 0(2.5) | 0(2.5) | 0(2.5) | 0(3.5) | 0(3.5) |

対応デバイス

AMD 7-Series, AMD Ultrascale, AMD Ultrascale+,Efinix Titanium,Efinix Topaz

カスタマイズ等のご要望についてはご相談下さい。

デモンストレーション環境

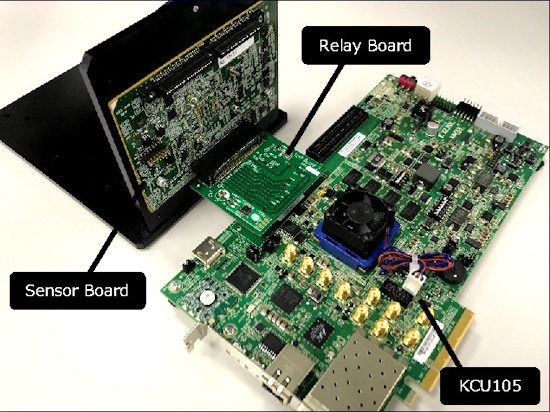

CISではSONYのIMX420センサーボードとAMDの評価ボードを接続するための中継基板と、各評価ボード用のリファレンスデザインを提供しております。例えばAC701を使用する場合は最大2レーン、KCU105とZCU106を使用する場合は最大8レーンで、Raw8、Raw10、Raw12のデモンストレーションを行うことができます。リファレンスデザインはお客様が自由にカスタマイズしてご使用頂けます。

また Efinix の Ti375N1156 評価ボード用のデモンストレーション環境も提供しております。

サポート体制

シーアイエスには各種高速インターフェースや画像処理に関連した RTL 設計、高速信号を含む基板設計、組み込みソフト開発などの分野で経験豊富なエンジニアが多数在籍しております。 IPのカスタマイズ等についてもお気軽にお問い合わせください。

製品紹介資料

SLVS-EC